#### K.S.R. COLLEGE OF ENGINEERING (Autonomous) <u>SEMESTER - VII</u>

#### ----

12EC3702

# EMBEDDED SYSTEM DESIGN

(Common to EC & IT)

#### Objective(s):

- To learn the basics of embedded computing platform, its hardware and software.

- To understand the concepts of processes and operating systems, for embedded system design.

- To gain knowledge about the concepts of hardware accelerators, networks and system design techniques in embedded system.

#### UNIT - I INTRODUCTION TO EMBEDDED ARCHITECTURE

Complex systems and Microprocessors - Embedded system design process - Formalisms for system design -Design example: Model train controller - Instruction sets preliminaries - ARM processor - CPU: Programming input and output - Supervisor mode, Exception and traps – Co-processors- Memory system mechanism – CPU performance - CPU power consumption.

#### UNIT - II COMPUTING PLATFORM AND DESIGN ANALYSIS

CPU buses - Memory devices - I/O devices - Component interfacing - Design with microprocessors - Development and debugging -Components for embedded programs- Model of programs - Assembly, Linking and loading - Basic compilation techniques -Program optimization - Program validation and testing.

#### UNIT - III PROCESSES AND OPERATING SYSTEMS

Multiple tasks and multi processes -Preemptive real time operating systems - Priority based scheduling -Inter process communication mechanisms - Evaluating operating system performance - Power management and optimization for processes.

#### UNIT - IV HARDWARE ACCELERATORS & NETWORKS

CPUs and accelerators -Multiprocessor performance analysis-Consumer electronics architecture -Distributed embedded architecture - Networks for embedded systems - Network based design -Internet enabled systems - Vehicles as networks - Sensor networks.

#### UNIT - V SYSTEM DESIGN TECHNIQUES

Design methodologies - Requirement analysis - Specifications - System analysis and architecture design - Quality assurance - Software tools for embedded system development- Design example: Alarm clock, Software modem, Elevator controller.

#### **Text Books:**

- 1. Wayne Wolf, "Computers as Components Principles of Embedded Computing System Design", Morgan Kaufmann Publisher, 2<sup>nd</sup> Edition, 2011.

- 2. Raj Kamal, "Embedded Systems Architecture, Programming and Design", Tata McGraw Hill, 2<sup>nd</sup> Edition, 2008.

#### **References:**

- 1. David E Simon, "An Embedded Software Primer", Pearson Education, 2007.

- 2. K.V.K.K.Prasad, "Embedded Real-Time Systems: Concepts, Design & Programming", Dreamtech Press, 2005.

- 3. Sriram V Iyer, Pankaj Gupta, "Embedded Real Time Systems Programming", TMG, 2004.

- 4. Tammy Noergaard, "Embedded Systems Architecture", Elsevier, 2006.

#### **Total hours: 45**

# 09 Hrs

09 Hrs

LTPC

0 3

3 0

### 09 Hrs

09 Hrs

09 Hrs

# K.S.R.COLLEGE OF ENGINEERING (AUTONOMOUS), TIRUCHENGODE-637215 DEPARTMENT OF ELECTRONICS COMMUNICATION AND ENGINEERING **COURSE / LESSION PLAN SCHEDULE**

| NAME    | : C.ARUNPRASATH, R.MAHENDRAN         | CLASS | : FINAL ECE |

|---------|--------------------------------------|-------|-------------|

| SUBJECT | : 12EC3702 / EMBEDDED SYSTEMS DESIGN | SEM   | : VII       |

#### A.TEXT BOOKS:

- 1. Wayne Wolf, "Computers as Components; Principles of Embedded Computing System Design", Morgan Kaufmann Publisher, 2<sup>nd</sup> Edition, 2011.

- 2. Raj Kamal, "Embedded Systems Architecture Programming and Design" 2nd Edition TMH, 2008.

# **B. REFERENCE:**

- 1. David E Simon "An Embedded Software Primer " Pearson Education ,2007.

- 2. K.V.K.K.Prasad "Embedded Real-Time Systems: Concepts, Design and Programming" Dreamtech press 2005.

- 3. Sriram V Iyer, Pankaj Gupta, "Embedded Real Time Systems Programming", TMG, 2004.

- 4. Tammy Noergaard, "Embedded System Architecture", Elsevier, 2006.

#### C. LEGEND:

| L    | - | Lecture                          | BB | - | Block Board    |

|------|---|----------------------------------|----|---|----------------|

| OHP  | - | Over Head Projector              | Тx | - | Text Book      |

| рр   | - | Pages                            | Rx | - | Reference Book |

| LCDP | - | Liquid Crystal Display Projector |    |   |                |

| S.No Lecture<br>Hour |                                                  |                                                                                 | Teaching  |                  |  |

|----------------------|--------------------------------------------------|---------------------------------------------------------------------------------|-----------|------------------|--|

|                      |                                                  | Topics to be covered                                                            | Aid       | Book No /Page No |  |

|                      |                                                  |                                                                                 | Required  |                  |  |

|                      | UNIT I - INTRODUCTION TO EMBEDDED ARCHITECTURE   |                                                                                 |           |                  |  |

| 1                    | L1                                               | Complex systems and Microprocessors                                             | BB        | Tx1-pp(2-9)      |  |

| 2.                   | L2                                               | Embedded system design process                                                  | BB, LCDP  | Tx1-pp(10-21)    |  |

| 3.                   | L3                                               | Formalisms for system design                                                    | BB        | Tx1-pp(21-32)    |  |

| 4.                   | L4                                               | Design example: Model train controller                                          | BB        | Tx1-pp(32-46)    |  |

| 5                    | L5                                               | Instruction sets preliminaries                                                  | BB        | Tx1-pp(57-62)    |  |

| 6                    | L6                                               | ARM Processor                                                                   | BB , LCDP | Tx1-pp(62-82)    |  |

| 7                    | L7                                               | CPU: Programming input and output                                               | BB        | Tx1-pp(105-128)  |  |

| 8                    | L8                                               | Supervisor modes, Exception and traps-co-                                       | BB        | Tx1-pp(128-144)  |  |

| 0                    | LO                                               | processors-Memory system mechanism                                              |           |                  |  |

| 9                    | 9 L9                                             | CPU Performance-CPU power consumption,                                          | BB        | Tx1-pp(144-158)  |  |

| 9 L9                 |                                                  | Testing tools                                                                   |           | Rx2-pp-66        |  |

|                      | UNIT II - COMPUTING PLATFORM AND DESIGN ANALYSIS |                                                                                 |           |                  |  |

| 10                   | L10                                              | CPU Buses                                                                       | BB, LCDP  | Tx1-pp(178-193)  |  |

| 11                   | L11                                              | Memory devices                                                                  | BB, LCDP  | Tx1-pp(193-201)  |  |

| 11                   |                                                  |                                                                                 |           | Rx2-pp(39-42)    |  |

| 12                   | L12                                              | I/O Devices, Component interfacing                                              | BB        | Tx1-pp(202-212)  |  |

| 12                   |                                                  | To Devices, component interfacing                                               |           | Rx2-pp(42-48)    |  |

| 13                   | L13                                              | Design with microprocessors                                                     | BB        | Tx1-pp(212-220)  |  |

| 14                   | L14                                              | Development and debugging                                                       | BB        | Tx1-pp(220-228)  |  |

| 15                   | L15                                              | Components for embedded programs, Model of                                      | BB        | Tx1-pp(252-257)  |  |

| 15 L                 |                                                  | programs                                                                        |           | Tx2-pp(223-227)  |  |

| 16                   | L16                                              | Assembly, linking and loading                                                   | BB        | Tx1-pp(258-265)  |  |

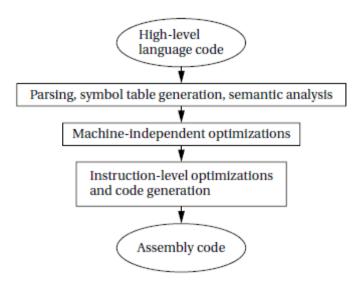

| 17                   | L17                                              | Basic compilation techniques                                                    | BB        | Tx1-pp(265-290)  |  |

| 18                   | L18                                              | Program optimization, Program validation and testing, <b>Productivity tools</b> | BB        | Tx1-pp(305-325)  |  |

| UNIT III - PROCESSES AND OPERATING SYSTEMS |          |                                                   |          |                              |

|--------------------------------------------|----------|---------------------------------------------------|----------|------------------------------|

| 19                                         | L19      | Multiple tasks and multi processes                | BB, LCDP | Tx1-pp(343-351)              |

| 20                                         | L20      | Preemptive real time operating systems            | BB       | Tx1-pp-356                   |

| 21                                         | L21      | Priority based scheduling                         | BB       | Tx1-pp-358                   |

| 22                                         | L22, L23 | Inter process communication mechanisms            | BB       | Tx1-pp(387-393)              |

| 23                                         | L24      | Evaluating operating system performance           | BB       | Tx1-pp(393-396)              |

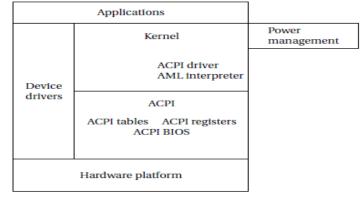

| 24                                         | L25      | Power management                                  | BB       | Tx1-pp(396-400)              |

| 25                                         | L26      | Optimization for processes                        | BB       | Tx1-pp-(262-267)             |

| 26                                         | L27      | Assembly language programming.                    | BB       | Tx2-pp-147                   |

|                                            |          | UNIT IV - HARDWARE ACCELERATORS AND               | NETWORKS |                              |

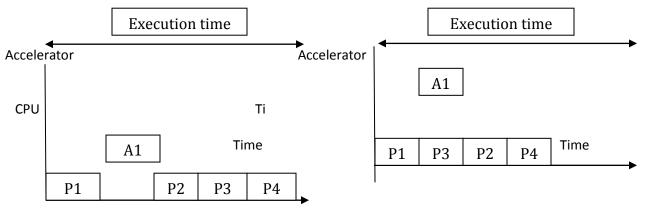

| 27                                         | L28      | CPUs and accelerators                             | BB       | Tx1-pp(420-423)              |

| 28                                         | L29      | Multiprocessor performance analysis               | BB       | Tx1-pp(424-437)              |

| 29                                         | L30      | Consumer electronics architecture                 | BB, LCDP | Tx1-pp-(369-373)             |

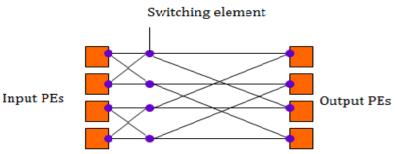

| 30                                         | L31      | Distributed embedded architecture                 | BB       | Tx1-pp(450-458)              |

| 31                                         | L32      | Network for embedded systems                      | BB       | Tx1-pp(458-475)              |

| 51                                         | LJZ      |                                                   | 66       | Tx2-pp(114-118)              |

| 32                                         | L33      | Network based design                              | BB       | Tx1-pp(475-484)              |

| 33                                         | L34      | Internet enabled systems                          | BB       | Tx1-pp(484-486)              |

| 34                                         | L35      | Vehicles as networks                              | BB, LCDP | Tx1-pp-(421-426)             |

| 35                                         | L36      | Sensor networks, Video accelerator                | BB       | Tx1-pp(437-445)              |

|                                            |          | UNIT V - SYSTEM DESIGN TECHNIQ                    | JES      |                              |

| 36                                         | L37      | Design methodologies                              | BB, LCDP | Tx1-pp(498-507)              |

| 50                                         | L37      |                                                   |          | Rx2-pp(99-102)               |

| 37                                         | L38      | Requirement analysis                              | BB       | Tx1-pp(507-508)              |

|                                            |          |                                                   |          | Rx2-pp(102-104)              |

| 38                                         | L39      | Specifications                                    | BB       | Tx1-pp(509-515)              |

| 39                                         | L40      | System analysis and architecture design           | BB       | Tx1-pp(515-520)              |

| 40                                         | L41      | Quality assurance                                 | BB       | Tx1-pp(520-534)              |

| 41                                         | L42      | Software tools for embedded system<br>development | BB       | Tx2-pp(34-36)                |

| 42                                         | L43      | Design example: Alarm clock                       | BB, LCDP | Tx1-pp(233-241)              |

| 43                                         | L44      | Software Modem                                    | BB, LCDP | Tx1-pp(325-330)              |

| 44                                         | L45      | Elevator Controller, Telephone PBX                | BB, LCDP | Tx1-pp(486-493)<br>(534-539) |

### K.S.R.COLLEGE OF ENGINEERING (AUTONOMOUS), TIRUCHENGODE-637215 DEPARTMENT OF ELECTRONICS COMMUNICATION AND ENGINEERING <u>12EC3702 - EMBEDDED SYSTEM DESIGN</u> QUESTION BANK

# UNIT - I

#### **INTRODUCTION TO EMBEDDED ARCHITECTURE**

#### 2 MARKS:

#### 1. What is an Embedded System? (Remembering) (CO1)

An embedded system can be defined as an computing device that does a specific focused job. E.g. Air-conditioner, VCD payer, DVD player, printer, fax machine, mobile phone, etc.

#### 2. List some application area of embedded systems? (Analyzing) (CO1)

Consumer appliances, industrial automation, medical electronics, computer networking, telecommunications, wireless technologies, instrumentations, security, finance.

#### 3. How an embedded system is categorized? (Remembering) (CO1)

Based on the functionality and performance requirements, embedded system can be categorized as: Stand-alone system, Real-time system, Networked information application, Mobile devices.

#### 4. What is Stand-alone embedded systems? (Remembering) (CO1)

Stand-alone systems works in Stand-alone mode. They take inputs, process them and produced the desired output, Example LCD and LED Display.

#### 5. What is real time systems? (Remembering) (CO1)

Embedded systems in which some specific work has to be done in a specific time period is called real-time systems. They are of two types,

a. Hard real time systems, b. Soft real time systems.

#### 6. What is networked information appliances? (Remembering) (CO1)

Embedded systems that are provided with network interfaces and accessed by networks such as local area network or the internet are called networked information appliances.

#### 7. What are the typical characteristics of an embedded system? (Remembering) (CO1)

- Sophisticated functionality.

- Real-time operation.

- Low manufacturing cost.

- Low power.

- Designed to tight deadlines by small teams.

#### 8. What are the real-time requirements of an embedded system? (Remembering) (CO1)

#### Hard-real time systems: where there is a high penalty for missing a deadline

**e.g.,** control systems for aircraft/space probes/nuclear reactors; refresh rates for video, or DRAM.

**Soft real time systems:** where there is a steadily increasing penalty if a deadline is missed. **e.g.**, laser printer: rated by pages-per-minute, but can take differing times to print a page (depending on the \"complexity\" of the page) without harming the machine or the customer.

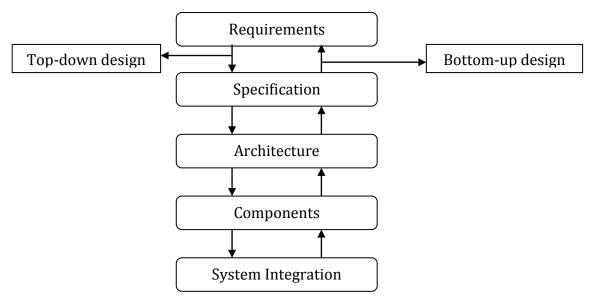

#### 9. Compare top-down and bottom-up design. (Analyzing)(AU-April 2014) (CO1)

#### **Top-Down:**

- Top down design proceeds from the abstract entity to get to the concrete design.

- It is most often used in designing brand new systems.

#### **Bottom-Up:**

- Bottom-up design proceeds from the concrete design to get to the abstract entity.

- It is sometimes used when one is reverse engineering a design, (i.e) when one is trying to figure out what somebody else designed in an existing design.

# **10.** What are the ways to design a digital system in embedded computers? (Remembering) (CO1) There are many ways to design a digital system. They are,

- (i). Custom logic (ii). Field Programmable Gate Array (FPGA)..Etc

- **11.** Discuss various issues in real time computing. (Creating)(AU-Nov/Dec 2013) (CO1) The various issues in RT computing is :

- Real -time Response

- Recovering from failures

- Working with distributed architecture

- Asynchronous communication

- Race condition and timing.

### 12. Define microprocessor. (Remembering) (CO1)

A microprocessor fetches and processes the set of general-purpose instructions such as data transfer, ALU operations, stack operations, I/O operations and other program control operations.

### 13. Why we use microprocessor in embedded computing process? (Remembering) (CO1)

(i). Microprocessor are a very efficient way to implement digital systems.

(ii). Microprocessor makes it easier to design families of products that can be built to provide various feature sets at different price points and can be extended to provide new features to keep up with rapidly changing networks.

# 14. List the challenges faced in embedded computing system design? (Analyzing) (June 2016) (CO1)

- (i). How much hardware do we need?

- (ii). How do we meet our deadlines?

- (iii). How do we minimize power consumption?

- (iv). How do we design for upgradeability?

- (v). Does it really work?

# 15. What are major goals of the embedded system design process? (Remembering) (CO1)

- Performance (both Overall speed and deadlines)

- Functionality and user interface.

- Manufacturing cost.

- Power consumption.

- Other requirements (physical size, etc.)

#### 16. Show some examples of functional requirements? (Understanding) (CO1)

- Performance

- Cost

- Physical size and weight

- Power consumption

- 17. What are the steps or levels of abstraction involved in the embedded system design process? (Remembering) (CO1)

# 18. What is mean by requirements and its types? (Remembering) (CO1)

Before designing a system, it must to understand what has to be designed. This can be known from the starting steps of a design process.

It can be classified into two types. They are

(i). Functional requirements - It says the fundamental functions of a system.

(ii). Non functional requirements – It deals with the certain parameters to be considered in an embedded systems.

# 19. How validating requirements are used in embedded system design process? (Remembering) (CO1)

Validating is a set of requirements is ultimately a psychological task since it requires understanding both what people want and how they communicate those needs. One good way to refine at least the user interface portion of a system's requirements is to build a mock-up.

The mock-up may use canned data to simulate functionality in a restricted demonstration, and it may be executed on a PC or a workstation.

# 20. What is the use of requirements form? (Remembering) (CO1)

It is used as a checklist in the requirements analysis. From this the fundamental properties of a system came to be known.

# 21. What are the entries of a requirement form? (Remembering) (CO1)

- Name

- Purpose

- Inputs and outputs

- Functions

- Performance

- Manufacturing cost

- Power

- Physical size and weight

# 22. What is meant by specification? (Remembering) (CO1)

This is a contract between the Customer and the Architect. It conveys the customer's needs. These needs are properly used in the design process.

# 23. What are the various components considered in the specification of GPS system? (Remembering) (CO1)

- Data received from the GPS satellite constellation

- Map data

- User interface

- Operations that must be performed to satisfy customer requests

- Background actions required to keep system running, such as operating the GPS receiver.

# 24. What is architecture design? (Remembering) (CO1)

It says the way of implementing functions by a system. Actually architecture is a plan for the overall structure of the system that will be used later to design the components that make up the architecture.

#### 25. What are the major components to satisfy the specification? (Remembering) (CO1)

There are two components are used to satisfy the specification. They are,

(i). **Hardware components:** It consists of CPU surrounded by memory and I/O devices. It may choose to use two memories. A frame buffer for the pixels to be displayed and a separate program/data memory for general use by the CPU.

(ii). **Software component:** It consists of timer to control when we read the buttons on the user interface and render data onto the screen.

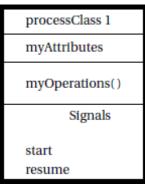

#### 26. Define UML (Unified Modeling Language). (Remembering) (CO1)

UML is an object oriented modeling language. It is a visual language that can be used to capture all these design tasks. It was designed to be useful at many levels of abstraction in the design process and it encourages design by successive refinement & progressively adding detail to the design.

# 27. Define system integration? (Remembering) (CO1)

It is a processor of combining the components into one system.

# 28. What is the importance of object oriented system design? (Remembering) (CO1)

(i). It encourages the design to be described as a number of interacting objects.

(ii). Design in terms of actual objects helps to understand the natural structure of the system.

# 29. Define class (Remembering) (CO1)

It is defined as the operation that determines how the object interacts with the rest of the world. All objects are derived from the same class have the same characteristics, although their attributes may have different values.

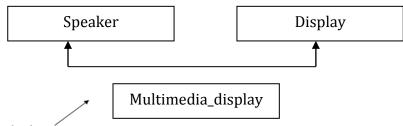

### 30. Explain the types of relationship between objects and classes. (Understanding) (CO1)

Association: objects communicate but one does not own the other.

Aggregation: a complex object is made of several smaller objects.

**Composition:** type of aggregation in which owner does not allow access to its components. **Generalization:** define one class in terms of another.

# 31. What is derived class? (Remembering) (CO1)

A derived class inherits all the attributes and operations from its base class.

#### 32. What is mean by link and association? (Remembering) (CO1)

Link - describe a relationship between objects

Association - describes relationship between classes.

# **33.** Define multiple inheritances. (Remembering) (CO1)

It is defined as in which a class is derived from more than one base class.

derived class

#### 34. What is mean by stereo type in UML language? (Remembering) (CO1)

It is a combination of elements in an object or class many times; we can give these patterns names, which are called stereotype in UML.

The stereotype name is written in the form <<signal>>

# 35. Classify the types of events in behavioral description in UML language. (Understanding) (CO1)

There are three events in behavioral description. They are,

- (i). Signal-asynchronous event.

- (ii). **Call**-follows the model of a procedure call in a programming language (Synchronized communication).

- (iii). **Time-out**-causes the machine to leave a state after a certain amount of time.

- 36. What is the relationship between an object-oriented specification and an object oriented programming language? (Remembering) (CO1)

A specification language may not be executable. But both object-oriented specification and programming languages provide similar basic methods for structuring large systems.

#### 37. Explain sequence diagram. (Understanding) (CO1)

A sequence diagram is somewhat similar to a hardware timing diagram, although the time flows vertically in a sequence diagram, whereas time typically flows horizontally in a timing diagram. The sequence diagram is designed to show a particular scenario or choice of events-it

is not convenient for showing a number of mutually exclusive possibilities. In this case, the sequence shows what happens when a mouse click is on the menu region.

# 38. List out the basic requirements of Model Train controller. (Analyzing) (CO1)

- The console shall be able to control up to eight trains on a single track.

- The speed of each train shall be controllable by a throttle to at least 63 different levels in each direction (forward and reverse).

- There shall be an inertia control that shall allow the user to adjust the responsiveness of the train to commanded changes in speed. Higher inertia means that the train responds more slowly to a change in the throttle, simulating the inertia of a large train. The inertia control will provide at least eight different levels.

- There shall be an emergency stop button.

- An error detection scheme will be used to transmit messages.

# 39. List the requirements model for Model train controller model. (Analyzing) (CO1)

| Name                   | -     | Model train controller                                   |

|------------------------|-------|----------------------------------------------------------|

| Purpose                | -     | Control speed of up to eight model trains                |

| Inputs                 | -     | Throttle, inertia setting, emergency stop, train number  |

| Outputs                | -     | Train control signals                                    |

| Functions              | -     | Set engine speed based upon inertia settings; respond to |

|                        |       | emergency stop                                           |

| Performance            | -     | Can update train speed at least 10 times per second      |

| Manufacturing cost     | -     | \$50                                                     |

| Power                  | -     | 10W (plugs into wall)                                    |

| Physical size and weig | ght - | Console should be comfortable for two hands, approximate |

|                        |       | size of standard keyboard; weight <2 pounds.             |

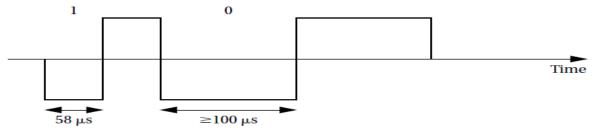

# 40. Classify the different types of documents used in DCC in controller. (Analyzing) (CO1)

The DCC standard is given in two documents:

(i). Standard S-9.1, the DCC Electrical Standard, defines how bits are encoded on the rails for transmission.

(ii).Standard S-9.2, the DCC Communication Standard, defines the packets that carry information.

# 41. How the voltage and power can be take part in the DCC electrical standard? (Remembering) (CO1)

The Electrical Standard deals with voltages and currents on the track. The data signal swings between two voltages around the power supply voltage. The bits are encoded in the time between transitions, not by voltage levels. A 0 is at least 100  $\mu$ s while a 1 is nominally 58  $\mu$ s.

The durations of the high (above nominal voltage) and low (below nominal voltage) parts of a bit are equal to keep the DC value constant. The specification also gives the allowable variations in bit times that a conforming DCC receiver must be able to tolerate. The standard also describes other electrical properties of the system, such as allowable transition times for signals.

### 42. Define DCC (Digital Command Control) in controller. (Remembering) (CO1)

The Digital Command Control (DCC) standard was created by the National Model Railroad Association to support interoperable digitally-controlled model trains. Hobbyists started building homebrew digital control systems in the 1970s and Marklin developed its own digital control system in the 1980s. DCC was created to provide a standard that could be built by any manufacturer so that hobbyists could mix and match components from multiple vendors.

# 43. Inspect the basic packet format for DCC communication standards. (Analyzing) (CO1)

We can write the basic packet format as a regular expression:

#### PSA (sD) + E

*P* is the preamble, which is a sequence of at least 10 1 bits. The command station should send at least 14 of these 1 bits, some of which may be corrupted during transmission.

*S* is the packet start bit. It is a 0 bit.

A is an address data byte that gives the address of the unit, with the most significant bit of the address transmitted first. An address is eight bits long.

The addresses 00000000, 11111110, and 11111111 are reserved.

*s* is the data byte start bit, which, like the packet start bit, is a 0.

*D* is the data byte, which includes eight bits. A data byte may contain an address, instruction, data, or error correction information.

*E* is a packet end bit, which is a 1 bit.

# 44. What type of packets used in Digital Command Control? (Remembering) (CO1) Baseline packet:

A **baseline packet** is the minimum packet that must be accepted by all DCC implementations. More complex packets are given in a Recommended Practice document.

- A baseline packet has three data bytes:

- an address data byte that gives the intended receiver of the packet;

- the instruction data byte provides a basic instruction; and

- an error correction data byte is used to detect and correct transmission errors.

#### 45. Discuss about Von Neumann and Harvard Architecture. (Creating) (CO1)

#### Von Neumann architecture:

• A computer whose memory holds both data and instructions is known as a **von Neumann** machine.

- The *program counters (PC)*, which holds the address in memory of an instruction.

- The CPU fetches the instruction from memory, decodes the instruction, and executes it.

#### Harvard Architecture:

- Harvard machine has separate memories for data and program.

- The program counter points to program memory, not data memory. As a result, it is harder to write self-modifying programs (programs that write data values, and then use those values as instructions) on Harvard machines.

#### 46. Explain RISC and CISC. (Understanding) (CO1)

#### **RISC (reduced instruction set computers):**

These computers tended to provide somewhat fewer and simpler instructions. The instructions were also chosen so that they could be efficiently executed in *pipelined* processors. Early RISC designs substantially outperformed CISC designs of the period. As it turns out, we can use RISC techniques to efficiently execute at least a common subset of CISC instruction sets, so the performance gap between RISC-like and CISC-like instruction sets has narrowed somewhat. **CISC (complex instruction set computers):**

These machines provided a variety of instructions that may perform very complex tasks, such as string searching; they also generally used a number of different instruction formats of varying lengths.

# 47. List out the variety of characteristics used in instruction set preliminaries. (Analyzing) (CO1)

Instructions can have a variety of characteristics, including:

- Fixed versus variable length.

- Addressing modes.

- Numbers of operands.

- Types of operations supported.

# 48. Define Programming Model. (Remembering) (CO1)

The set of registers available for use by programs is called the programming model, also known as the programmer model. (The CPU has many other registers that are used for internal operations and are unavailable to programmers.)

### 49. Analyze some features or parameter used in assembly language. (Analyzing) (CO1)

Assembly languages usually share the same basic features:

- One instruction appears per line.

- *Labels*, which give names to memory locations, start in the first column.

- Instructions must start in the second column or after to distinguish them from labels.

- Comments run from some designated comment character (; in the case of ARM) to the end of the line.

### 50. Explain about ARM processor. (Understanding) (AU-Nov/Dec 2013) (CO1)

ARM – Advanced RISC Machine. (It is an 32-bit Microprocessor)

ARM is actually a family of RISC architectures that have been developed over many years. The ARM is a 32-bit Reduced Instruction Set Computer (RISC) instruction set architecture developed by Arm holdings. ARM processor is mad suitable for Low power application.

ARM is actually a family of RISC architectures that have been developed over many years. ARM does not manufacture its own VLSI devices; rather, it licenses its architecture to companies who either manufacture the CPU itself or integrate the ARM processor into a larger system.

# 51. List the functions of ARM processor in supervisor mode. (Analyzing)(AU-April 2014) (CO1)

The various functions of ARM processor in supervisor modes are:

- Exception

- Prioritization

- Vectoring

- Traps.

#### 52. Define Assembly language. (Remembering) (CO1)

The textual description of instructions, as opposed to their binary representation, is called an assembly language.

#### 53. List some example program for ARM processor using assembly language. (Analyzing) (CO1)

ARM instructions are written one per line, starting after the first column. Comments begin with a semicolon and continue to the end of the line. A label, which gives a name to a memory location, comes at the beginning of the line, starting in the first column. Here is an example:

LDR r0,[r8]; a comment

label ADD r4,r0,r1

# 54. Identify the versions used in ARM processor with different architecture. (Applying) (CO1)

- ARM7 is a von Neumann architecture machine

- ARM9 uses a Harvard architecture.

- However, this difference is invisible to the assembly language programmer, except for possible performance differences.

# 55. Classify the different types of data used in ARM architecture. (Understanding) (CO1)

- The ARM architecture supports two basic types of data:

- The standard ARM word is 32 bits long.

- The word may be divided into four 8-bit bytes.

ARM7 allows addresses up to 32 bits long. An address refers to a byte, not a word. Therefore, the word 0 in the ARM address space is at location 0, the word 1 is at 4, the word 2 is at 8, and so on. (As a result, the PC is incremented by 4 in the absence of a branch.)

# 56. What is the Instruction set features useful for embedded programming? (Remembering) (AU-May/June 2013) (CO1)

Instruction Sets can have a variety of characteristics/features including:

- Fixed versus variable length

- Addressing modes

- Number of operands

- Types of operations supported.

# 57. What are the different types of data operations used in ARM Processor? (Remembering) (CO1)

- Arithmetic and logical operations (ADD-Add, ADC-Add with carry, SUBC-Subtract with carry, etc.,)

- Load and store instructions (LDR-Load, STR-Store, LDRH- Load half word, etc.,)

- Shift/rotate instruction (LSL-Logical shift left, LSR-Logical shift right, etc.,)

- ARM comparison instruction (CMP-Compare, CMN-Negated compare, TST-Bit wise test, TEQ-Bit wise negated test)

- Move instruction (MOV-Move, MVN-Move negated)

# 58. What is meant by current program status register (CPSR) and represent its bits? (Remembering) (CO1)

The other important basic register in the programming model is the current program status register (CPSR). This register is set automatically during every arithmetic, logical, or shifting operation.

The top four bits of the CPSR hold the following useful information about the results of that arithmetic/logical operation:

- The negative (N) bit is set when the result is negative in two's-complement arithmetic.

- The zero (Z) bit is set when every bit of the result is zero.

- The carry (C) bit is set when there is a carry out of the operation.

- The overflow (V) bit is set when an arithmetic operation results in an overflow.

# 59. Define branch instructions. (Remembering) (CO1)

The B (branch) instruction is the basic mechanism in ARM for changing the flow of control. The address that is the destination of the branch is often called the branch target. Branches are PC-relative—the branch specifies the offset from the current PC value to the branch target. The offset is in words, but because the ARM is byte addressable, the offset is multiplied by four (shifted left two bits, actually) to form a byte address. Thus, the instruction

#### B #100

Will add 400 to the current PC value.

# 60. What is programmable input and output devices and also mention the registers in I/P & O/P devices? (Remembering) (CO1)

Input and output devices usually have some analog or non electronic component-for instance, a disk drive has a rotating disk and analog read/write electronics. But the digital logic in the device that is most closely connected to the CPU very strongly resembles the logic you would expect in any computer system.

The interface between the CPU and the device's internals (e.g., the rotating disk and read/write electronics in a disk drive) is a set of registers. The CPU talks to the device by reading and writing the registers. Devices typically have several registers:

• **Data registers** hold values that are treated as data by the device, such as the data read or written by a disk.

• **Status registers** provide information about the device's operation, such as whether the current transaction has completed.

# 61. How Microprocessors can provide programming support for input and output devices? (Remembering) (CO1)

Microprocessors can provide programming support for input and output in two ways:

- I/O instructions

- memory-mapped I/O

Some architectures, such as the Intel x86, provide special instructions (in and out in the case of the Intel x86) for input and output. These instructions provide a separate address space for I/O devices.

But the most common way to implement I/O is by memory mapping-even CPUs that provide I/O instructions can also implement memory-mapped I/O. As the name implies, memory-mapped I/O provides addresses for the registers in each I/O device.

### 62. Define polling or Busy-Wait I/O (Remembering) (June 2016) (CO1)

The most basic way to use devices in a program is *busy-wait I/O*. Devices are typically slower than the CPU and may require many cycles to complete an operation.

If the CPU is performing multiple operations on a single device, such as writing several characters to an output device, then it must wait for one operation to complete before starting the next one. (If we try to start writing the second character before the device has finished with the first one, for example, the device will probably never print the first character.) Asking an I/O device whether it is finished by reading its status register is often called **polling**.

# 63. What is meant by Interrupt and interrupt handler or device driver? (Remembering) (CO1) Interrupt:

The interrupt mechanism allows devices to signal the CPU and to force execution of a particular piece of code.

#### Interrupt handler or device driver:

When an interrupt occurs, the program counter's value is changed to point to an interrupt handler routine (also commonly known as a device driver) that takes care of the device: writing the next data, reading data that have just become ready, and so on. The interrupt mechanism of course saves the value of the PC at the interruption so that the CPU can return to the program that was interrupted. Interrupts therefore allow the flow of control in the CPU to change easily between different contexts, such as a foreground computation and multiple I/O devices.

# 64. List out the interface between the CPU and I/O device includes the following signals for interrupting. (Analyzing) (CO1)

- The I/O device asserts the *interrupt request* signal when it wants service from the CPU; and

- The CPU asserts the *interrupt acknowledge* signal when it is ready to handle the I/O device's request.

#### 65. Define foreground program. (Remembering) (CO1)

The program that runs when no interrupt is being handled is often called the foreground program; when the interrupt handler finishes, it returns to the foreground program, wherever processing was interrupted.

#### 66. Explain about priorities and vectors. (Understanding) (CO1)

Providing a practical interrupt system requires having more than a simple interrupt request line. Most systems have more than one I/O device, so there must be some mechanism for allowing multiple devices to interrupt. We also want to have flexibility in the locations of the interrupt handling routines, the addresses for devices, and so on.

There are two ways in which interrupts can be generalized to handle multiple devices and to provide more flexible definitions for the associated hardware and software:

- Interrupt priorities allow the CPU to recognize some interrupts as more important than others, and

- *Interrupt vectors* allow the interrupting device to specify its handler.

#### 67. Define masking. (Remembering) (CO1)

The priority mechanism must ensure that a lower-priority interrupt does not occur when a higher-priority interrupt is being handled. The decision process is known as **masking**.

The highest-priority interrupt is normally called the **non maskable interrupt (NMI)**. The NMI cannot be turned off and is usually reserved for interrupts caused by power failures-a simple circuit can be used to detect a dangerously low power supply, and the NMI interrupt handler can be used to save critical state in nonvolatile memory, turn off I/O devices to eliminate spurious device operation during power down, and so on.

# 68. What is meant by Interrupt overhead and determine the steps involved in the process? (Remembering) (CO1)

Now that we have a basic understanding of the interrupt mechanism, we can consider the complete interrupt handling process. Once a device requests an interrupt, some steps are performed by the CPU, some by the device, and others by software. Here are the major steps in the process:

• **CPU:** The CPU checks for pending interrupts at the beginning of an instruction. It answers the highest-priority interrupt, which has a higher priority than that given in the interrupt priority register.

• Device: The device receives the acknowledgment and sends the CPU its interrupt vector.

• **CPU:** The CPU looks up the device handler address in the interrupt vector table using the vector as an index. A subroutine-like mechanism is used to save the current value of the PC and possibly other internal CPU state, such as general-purpose registers.

• **Software:** The device driver may save additional CPU state. It then performs the required operations on the device. It then restores any saved state and executes the interrupt return instruction.

• **CPU:** The interrupt return instruction restores the PC and other automatically saved states to return execution to the code that was interrupted.

# 69. Describe about the interrupt used in ARM7. (CO1)

ARM7 supports two types of interrupts:

- Fast interrupt requests (FIQs) and

- Interrupt requests (IRQs).

An FIQ takes priority over an IRQ. The interrupt table is always kept in the bottom memory addresses, starting at location 0.The entries in the table typically contain subroutine calls to the appropriate handler.

# 70. Develop the steps involved in the interrupt in ARM7 processor. (Applying) (CO1)

The ARM7 performs the following steps when responding to an interrupt

- Saves the appropriate value of the PC to be used to return,

- Copies the CPSR into a saved program status register (SPSR),

- Forces bits in the CPSR to note the interrupt, and

- Forces the PC to the appropriate interrupt vector.

When leaving the interrupt handler, the handler should:

- Restore the proper PC value,

- Restore the CPSR from the SPSR, and

- Clear interrupt disable flags.

# 71. List out the interrupt used in C55xprocessor. (Analyzing) (CO1)

A maskable interrupt is processed in several steps once the interrupt request is sent to the CPU:

- The interrupt flag register (IFR) corresponding to the interrupt is set.

- The interrupt enable register (IER) is checked to ensure that the interrupt is enabled.

- The interrupt mask register (INTM) is checked to be sure that the interrupt is not masked.

- The interrupt flag register (IFR) corresponding to the flag is cleared.

- Appropriate registers are saved as context.

- INTM is set to 1 to disable maskable interrupts.

- DGBM is set to 1 to disable debug events.

- EALLOW is set to 0 to disable access to non-CPU emulation registers.

- A branch is performed to the interrupt service routine (ISR).

#### 72. Explain the mechanism used in C55x processor. (Understanding) (CO1)

The C55x provides two mechanisms

- fast-return and

- slow-return

To save and restore registers for interrupts and other context switches. Both processes save the return address and loop context registers.

The fast-return mode uses RETA to save the return address and CFCT for the loop context bits.

The slow return mode, in contrast, saves the return address and loop context bits on the stack.

# 73. What is meant by Supervisor mode, Exception and traps? (Remembering) (AU-Nov/Dec 2012) (AUT-Dec 2015) (CO1)

# Supervisor mode:

In such cases it is often useful to have a **supervisor mode** provided by the CPU. Normal programs run in **user mode**. The supervisor mode has privileges that user modes do not. **Exception:**

An **exception** is an internally detected error. A simple example is division by zero. One way to handle this problem would be to check every divisor before division to be sure it is not zero, but this would both substantially increase the size of numerical programs and cost a great deal of CPU time evaluating the divisor's value. The CPU can more efficiently check the divisor's value during execution. Since the time at which a zero divisor will be found is not known in advance, this event is similar to an interrupt except that it is generated inside the CPU. The exception mechanism provides a way for the program to react to such unexpected events. **Traps:**

A **trap**, also known as a **software interrupt**, is an instruction that explicitly generates an exception condition. The most common use of a trap is to enter supervisor mode.

# 74. What is the function of exception? (Remembering) (AU-Nov/Dec 2012) (CO1)

- The main function of exception is to detect the error internally.

- It requires both prioritization and vectoring.

# 75. Define co-processors. (Remembering) (CO1)

CPU architects often want to provide flexibility in what features are implemented in the CPU. One way to provide such flexibility at the instruction set level is to allow co-processors, which are attached to the CPU and implement some of the instructions.

For example, floating-point arithmetic was introduced into the Intel architecture by providing separate chips that implemented the floating-point instructions.

# 76. What is meant by cache in memory system techniques and its conditions? (Remembering) (CO1)

Caches are widely used to speed up memory system performance. A cache is a small, fast memory that holds copies of some of the contents of main memory.

A *cache controller* mediates between the CPU and the memory system comprised of the main memory. The cache controller sends a memory request to the cache and main memory.

If the requested location is in the cache, the cache controller forwards the location's contents to the CPU and aborts the main memory request; this condition is known as a *cache hit*.

If the location is not in the cache, the controller waits for the value from main memory and forwards it to the CPU; this situation is known as a *cache miss*.

#### 77. Classify the cache misses in memory system mechanisms. (Understanding) (CO1)

We can classify cache misses into several types depending on the situation that generated them:

- a compulsory miss (also known as a cold miss) occurs the first time an location is used,

- a capacity miss is caused by a too-large working set, and

- a **conflict miss** happens when two locations map to the same location in the cache.

# 78. Define bit rate and miss rate. (Remembering) (CO1)

Let h be the **hit rate**, the probability that a given memory location is in the cache. It follows that 1-h is the **miss rate**, or the probability that the location is not in the cache. Then we can compute the average memory access time as

$$t_{\rm av} = bt_{\rm cache} + (1 - b)t_{\rm main}$$

where  $t_{cache}$  is the access time of the cache and  $t_{main}$  is the main memory access time.

# 79. Classify the different types of levels in cache memory. (Understanding) (CO1)

- The first-level cache (commonly known as L1 cache) is closest to the CPU, the

- second-level cache (L2 cache) feeds the first-level cache, and so on.

# 80. Explain the term write through and write back in cache techniques. (Understanding) (CO1) Write through:

Every write changes both the cache and the corresponding main memory location (usually through a write buffer). This scheme ensures that the cache and main memory are consistent, but may generate some additional main memory traffic.

#### Write back:

We can reduce the number of times we write to main memory by using a *write-back* policy: If we write only when we remove a location from the cache, we eliminate the writes when a location is written several times before it is removed from the cache.

#### 81. Define unified cache (Remembering) (CO1)

A cache that holds both instructions and data is called a unified cache.

# 82. Define page fault (Remembering) (CO1)

When the CPU requests an address that is not in main memory, the MMU generates an exception called a page fault.

The program that generated the page fault is restarted by the handler only after,

- The required memory has been read back into main memory, and

- The MMU's tables have been updated to reflect the changes.

# 83. What is meant by address translation and its styles? (Remembering) (CO1)

A MMU translates addresses between the CPU and physical memory. This translation process is often known as *memory mapping* since addresses are mapped from a logical space into a physical space.

There are two styles of address translation:

- segmented and

- paged

Each has advantages and the two can be combined to form a segmented, paged addressing scheme. A segment is usually described by its start address and size, allowing different segments to be of different sizes. Pages are of uniform size, which simplifies the hardware required for address translation.

#### 84. Define translation lookaside buffer (TLB) (Remembering) (CO1)

The efficiency of paged address translation may be increased by caching page translation information. A cache for address translation is known as a translation lookaside buffer (TLB). The MMU reads the TLB to check whether a page number is currently in the TLB cache and, if so, uses that value rather than reading from memory.

# 85. What are memory regions for address translation in ARM MMU Techniques? (Remembering) (CO1)

ARM MMU supports the following types of memory regions for address translation:

- Section is a 1-MB block of memory,

- Large page is 64 KB, and

- Small page is 4 KB.

# 86. Define pipelining and list the different types of stages in this process. (Remembering) (CO1)

Modern CPUs are designed as pipelined machines in which several instructions are executed in parallel. Pipelining greatly increases the efficiency of the CPU. But like any pipeline, a CPU pipeline works best when its contents flow smoothly. Some sequences of instructions can disrupt the flow of information in the pipeline and, temporarily at least, slow down the operation of the CPU.

The ARM7 has a three-stage pipeline:

• **Fetch** the instruction is fetched from memory.

• **Decode** the instruction's opcode and operands are decoded to determine what function to perform.

- **Execute** the decoded instruction is executed.

- 87. What are the parameters used to evaluate the CPU performance? (Remembering )(AU-May/June 2013) (CO1)

- Pipelining and

- Caching.

### 88. Define latency and throughput. (Remembering) (CO1)

A normal instruction requires three clock cycles to completely execute, known as the **latency** of instruction execution.

But since the pipeline has three stages, an instruction is completed in every clock cycle. In other words, the pipeline has a **throughput** of one instruction per cycle.

#### 89. List the seven stages in C55x processor. (Analyzing) (CO1)

The C55x includes a seven-stage pipeline:

- Fetch.

- Decode.

- Address computes data and branch addresses.

- Access 1 reads data.

- Access 2 finishes data read.

- Read stage puts operands onto internal busses.

- Execute performs operations.

- 90. Explain the concept of CPU power consumption and its basic sources. (Understanding) (CO1)

The high-level power consumption characteristics of CPUs and other system components are derived from the circuits used to build those components. Today, virtually all digital systems are built with complementary metal oxide semiconductor (CMOS) circuitry.

The basic sources of CMOS power consumption is,

- Voltage drops: The dynamic power consumption of a CMOS circuit is proportional to the square of the power supply voltage (V2).

- Togging: A CMOS circuit uses most of its power when it is changing its output value.

- Leakage: Even when a CMOS circuit is not active, some charge leaks out of the circuit's nodes through the substrate.

#### 91. Classify the different types of power management provided by CPU. (Understanding) (CO1)

There are two types of power management features provided by CPUs.

A **static power management** mechanism is invoked by the user but does not otherwise depend on CPU activities. An example of a static mechanism is a power down mode intended to save energy. This mode provides a high-level way to reduce unnecessary power consumption.

A **dynamic power management** mechanism takes actions to control power based upon the dynamic activity in the CPU. For example, the CPU may turn off certain sections of the CPU when the instructions being executed do not need them.

# 92. How is ARM processor different from other processors? (Remembering)(AU-Nov/Dec 2012) (CO1)

- ARM is a RISC (Reduced Instruction Set Computing) architecture while other processor being a CISC (Computer Instruction Set Computing) one.

- In the ARM processor, arithmetic and logical operations cannot be perform directly on memory locations, while other processors allow such operations to directly reference main memory.

- 93. When is application specific system processor (ASSPs) used in embedded systems? (Remembering) (AU-May/June 2012) (CO1)

ASSP is a processing unit for specific task and for specific application. In embedded system for example image compression and that is integrated through the buses with the main processor in an embedded system.

- 94. What are the various in embedded system designs modeling refining (or) partitioning? (Remembering) (AU-May/June 2012) (CO1)

- Structural modeling

- Behavior modeling

- State machine modeling

- Process algebra modeling

- Logic based modeling

- Petri-nets modeling.

- 95. State the difference between top down and bottom up design approach in embedded system. (Evaluating) (Dec 2015) (CO1)

| TOP DOWN DESIGN                                  | BOTTOM UP DESIGN                            |

|--------------------------------------------------|---------------------------------------------|

| It will begin with the most abstract description | It starts with components to build a system |

| of the systems and conclude with details.        | decisions at one stage of design are based  |

|                                                  | upon estimates of what will happen later.   |

# **BIG QUESTIONS:**

- 1. Discuss in detail about complex systems and microprocessors. (Creating) (CO1)

- 2. Discuss about the requirements, specification and architectural design in the process of embedded system design. (Creating) (CO1) OR

Discuss the top down method embedded system design development with suitable example. (Creating) (June 2016) (CO1)

3. Explain in detail about various mechanisms in formalisms for system design. (Understanding) (CO1) OR

Discuss in detail about Structural and Behavioral description of methods used for designing an embedded system. (Creating) (AU-May/June 2013) (CO1)

- 4. List the description method in UML and explain any one method. (Analyzing) (June 2016) (CO1)

- 5. Classify the various stages involved in the design of model train controller. (Analyzing) (AU-Nov/Dec 2012, May/June 2013, April 2014) (CO1) OR

Draw a model train control system and elaborate about the specification using the class diagram. (Creating) (Dec 2015) (CO1)

- 6. Explain the design process details of an embedded system with some specific example. (Evaluating) (AU-Nov/Dec 2013) (CO1)

- 7. Explain in detail about instruction set preliminaries with examples. (Understanding) (AU-Nov/Dec 2013,Nov/Dec 2014) (CO1)

- 8. Discuss in detail the embedded system design by considering ARM processor and its memory organization as a design examples. (Creating) (AU-May/June 2013,Nov/Dec 2014) (CO1)

- 9. Explain in detail about different types of data operations in ARM Processor with examples. (Understanding)(AU-May/June 2013) (CO1)

- 10. Summarize the concept about programming input and output devices in CPU and its primitives. (Understanding) (CO1)

- 11. Explain the terms: Supervisor mode, Exceptions and Traps in detail. (Understanding) (AU-Nov/Dec 2013) (CO1)

- 12. What is Coprocessor? Write about its significance. (Remembering) (Dec 2015) (CO1)

- 13. Elaborate in detail about the Memory system mechanisms and its types. (Creating) (CO1)

- 14. How to evaluate CPU Performance? (Remembering) (AU-Nov/Dec 2014) (CO1)

- 15. Justify that what type of power can be consumed in CPU with different processors. **(Evaluating) (CO1)**

- 16. What are the various goals and tasks of the embedded system design process? Illustrate with an example. (Understanding) (Dec 2015) (CO1)

- 17. Describe the direct mapped and set associative cache map with examples. (Understanding) (June 2016) (CO1)

# <u>UNIT - II</u>

# COMPUTING PLATFORM AND DESIGN ANALYSIS

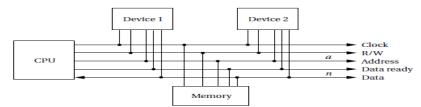

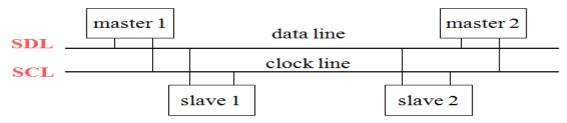

# 1. What is CPU Bus? (Remembering) (CO2)

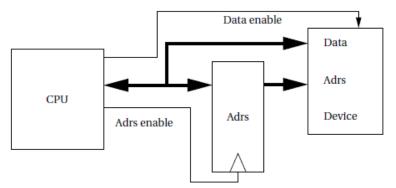

A computer system encompasses much more than the CPU; it also includes memory and I/O devices. The bus is the mechanism by which the CPU communicates with memory and devices. A bus is, at a minimum, a collection of wires, but the bus also defines a protocol by which the CPU, memory, and devices communicate.

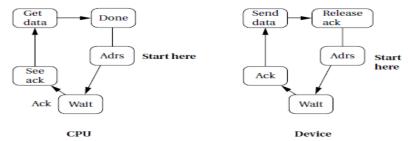

# 2. What is the major role of bus? (Remembering) (CO2)

One of the major roles of the bus is to provide an interface to memory.

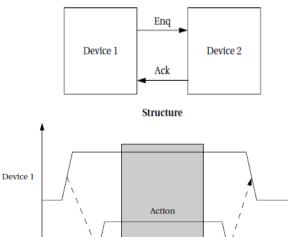

# 3. Construct basic building block of most bus protocols. (Applying) (CO2)

The basic building block of most bus protocols is the **four-cycle handshake** The handshake uses a pair of wires dedicated to the handshake: **enq** (meaning enquiry) and **ack** (meaning acknowledge). Extra wires are used for the data transmitted during the handshake.

# 4. What is four-cycle handshake? (Remembering) (June 2016) (CO2)

The four cycles are described below.

- 1. *Device* 1 raises its output to signal an enquiry, which tells *device* 2 that it should get ready to listen for data.

- 2. When *device 2* is ready to receive, it raises its output to signal an acknowledgment. At this point, *devices 1* and 2 can transmit or receive.

- 3. Once the data transfer is complete, *device 2* lowers its output, signaling that it has received the data.

- 4. After seeing that *ack* has been released, *device 1* lowers its output.

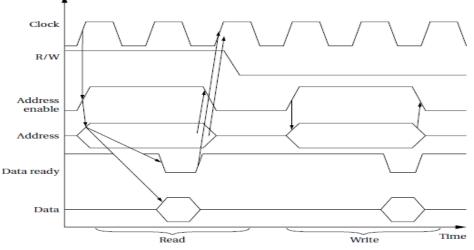

#### 5. List the fundamental operation of bus. (Analyzing) (CO2)

The fundamental bus operations are reading and writing.

#### 6. Define bus. (Remembering) (CO2)

The term *bus* is used in two ways. The most basic use is as a set of related wires, such as address wires. However, the term may also mean a protocol for communicating between components. To avoid confusion, we will use the term *bundle* to refer to a set of related signals.

7. Construct typical microprocessor bus. (Creating) (CO2)

# 8. What are the major components in microprocessor bus? (Remembering) (CO2)

The major components follow:

- Clock provides synchronization to the bus components,

- R/W is true when the bus is reading and false when the bus is writing,

- Address is an a-bit bundle of signals that transmits the address for an access,

- Data is an n-bit bundle of signals that can carry data to or from the CPU, and

- Data ready signals when the values on the data bundle are valid.

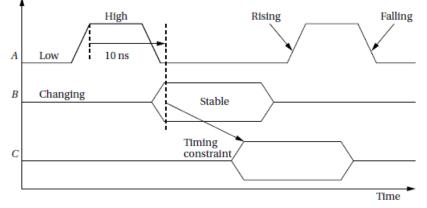

# 9. Infer timing diagram. (Understanding) (CO2)

The behavior of a bus is most often specified as a *timing diagram*. A timing diagram shows how the signals on a bus vary over time, but since values like the address and data can take on many values, some standard notation is used to describe signals.

# 10. Show the timing diagram notation. (Understanding) (CO2)

11. Show the timing diagram for the example bus. (Understanding) (CO2)

# 12. Examine data ready signal. (Analyzing) (CO2)

The data ready signal allows the bus to be connected to devices that are slower than the bus.

#### 13. Demonstrate the State diagrams for the bus read transaction. (Understanding) (CO2)

### 14. What are wait states? (Remembering) (CO2)

The cycles between the minimum time at which data can be asserted and when it is actually asserted are known as **wait states**. Wait states are commonly used to connect slow, inexpensive memories to buses.

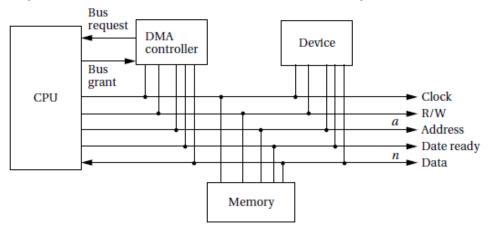

#### 15. What is Direct Memory Access (DMA)? (Remembering) (CO2)

Direct memory access (DMA) is a bus operation that allows reads and writes not controlled by the CPU.

#### 16. Explain about DMA controller. (Evaluating) (CO2)

A DMA transfer is controlled by a DMA controller, which requests control of the bus from the CPU.After gaining control, the DMA controller performs read and write operations directly between devices and memory.

#### 17. Examine bus signals for multiplexing address and data. (Analyzing) (CO2)

18. Show the configuration of a bus with a DMA controller. (Remembering) (CO2)

- 19. What are two additional bus signals that DMA requires the CPU to provide? (Remembering) (CO2)

- The **bus request** is an input to the CPU through which DMA controllers ask for ownership of the bus.

- The **bus grant** signals that the bus has been granted to the DMA controller.

#### 20. Summarize bus master. (Understanding) (CO2)

A device that can initiate its own bus transfer is known as a bus master. Devices that do not have the capability to be bus masters do not need to connect to a bus request and bus grant.

# 21. List the registers that are required in DMA controller for DMA operation. (Analyzing) (CO2)

The CPU controls the DMA operation through registers in the DMA controller. A typical DMA controller includes the following three registers:

- 1. A starting address register specifies where the transfer is to begin.

- 2. A length register specifies the number of words to be transferred.

- 3. A status register allows the DMA controller to be operated by the CPU.

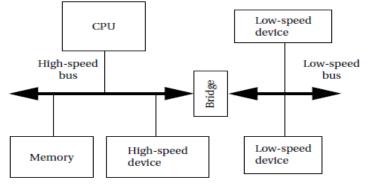

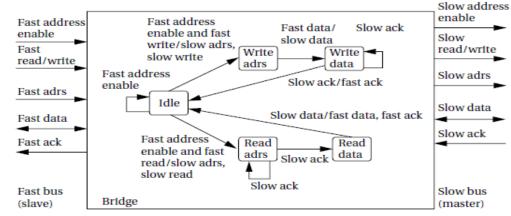

# 22. Define bridge. (Remembering) (CO2)

A small block of logic known as a bridge, allows the buses to connect to each other.

# 23. What are the reasons to use multiple buses and bridges? (Remembering) (CO2)

- Higher-speed buses may provide wider data connections.

- A high-speed bus usually requires more expensive circuits and connectors. The cost of low-speed devices can be held down by using a lower-speed, lower-cost bus.

- The bridge may allow the buses to operate independently, thereby providing some parallelism in I/O operations.

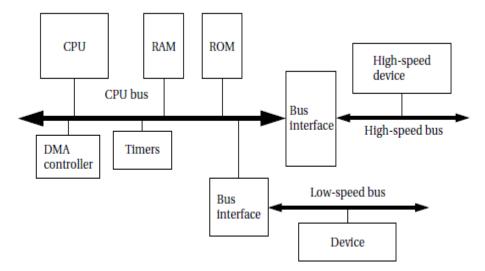

- 24. Build a multiple bus system.(Creating) (CO2)

#### 25. Outline UML state diagram of bus bridge operation. (Understanding) (CO2)

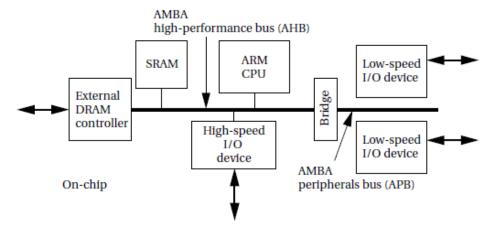

26. Show the elements of the ARM AMBA bus system. (Remembering) (CO2)

### 27. What is aspect ratio in memory? (Remembering) (CO2)

The height/width ratio of a memory is known as its aspect ratio. The best aspect ratio depends on the amount of memory required.

# 28. What is a RAM? (Remembering) (CO2)

Random Access Memories (RAM's) can be both read and written. They are called random access because, unlike magnetic disks, addresses can be read in any order.

# 29. What is DRAM? (Remembering) (CO2)

Most bulk memory in modern systems is dynamic RAM (DRAM). DRAM is very dense; it does, however, require that its values be refreshed periodically since the values inside the memory cells decay over time.

# 30. What is SRAM? (Remembering) (CO2)

The dominant form of dynamic RAM today is the Synchronous DRAMs (SDRAMs), which use clocks to improve DRAM performance. SDRAMs use Row Address Select (RAS) and Column Address Select (CAS) signals to break the address into two parts, which select the proper row and column in the RAM array. Signal transitions are relative to the SDRAM clock, which allows the internal SDRAM operations to be pipelined.

# 31. Write characteristics of SRAM and DRAM. (Remembering) (Dec 2015) (CO2)

- SRAM is faster than DRAM.

- SRAM consumes more power than DRAM.

- More DRAMs can be put on a single chip.

- DRAM values must be periodically refreshed.

# 32. Elaborate SIMMs and DIMMs. (Creating) (CO2)

Memory for PCs is generally purchased as Single In Line Memory Modules (SIMMs) or Double In Line Memory Modules (DIMMs). A SIMM or DIMM is a small circuit board that fits into a standard memory socket. A DIMM has two sets of leads compared to the SIMM's one. Memory chips are soldered to the circuit board to supply the desired memory.

### 33. What is ROM? (Remembering) (CO2)

Read Only Memories (ROMs) are preprogrammed with fixed data. They are very useful in embedded systems since a great deal of the code, and perhaps some data, does not change over time. Read-only memories are also less sensitive to radiation induced errors.

# 34. Distinguish factory programmed ROM or mask and field programmable ROM.(Evaluating) (June 2016) (CO2)

**Factory programmed ROMs or mask** are ordered from the factory with particular programming. ROMs can typically be ordered in lots of a few thousand, but clearly factory programming is useful only when the ROMs are to be installed in some quantity. They are sometimes called mask programmed ROM.

**Field-programmable ROMs**, on the other hand, can be programmed in the lab. Flash memory is the dominant form of field programmable ROM and is electrically erasable.

#### 35. What is flash memory? (Remembering) (CO2)

**Flash memory** is the dominant form of field-programmable ROM and is electrically erasable. Flash memory uses standard system voltage for erasing and programming, allowing it to be reprogrammed inside a typical system. This allows applications such as automatic distribution of upgrades - the flash memory can be reprogrammed while downloading the new memory contents from a telephone line.

#### 36. What is boot - block flash? (Remembering) (CO2)

Early flash memories had to be erased in their entirety; modern devices allow memory to be erased in blocks. Most flash memories today allow certain blocks to be protected. A common application is to keep the boot-up code in a protected block but allow updates to other memory blocks on the device. As a result, this form of flash is commonly known as boot-block flash.

#### 37. Distinguish Timers and counters (Evaluating). (CO2)

**Timers** and **counters** are distinguished from one another largely by their use, not their logic. Both are built from adder logic with registers to hold the current value, with an increment input that adds one to the current register value. However, a timer has its count connected to a periodic clock signal

to measure time intervals, while a counter has its count input connected to an aperiodic signal in order to count the number of occurrences of some external event. Because the same logic can be used for either purpose, the device is often called a **counter/timer**.

# 38. What is watchdog timer? (Remembering) (CO2)

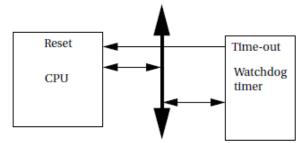

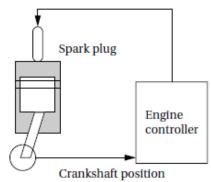

A *watchdog timer* is an I/O device that is used for internal operation of a system. As shown in Figure, the watchdog timer is connected into the CPU bus and also to the CPU's reset line. The CPU's software is designed to periodically reset the watchdog timer, before the timer ever reaches its time-out limit. If the watchdog timer ever does reach that limit, its time-out action is to reset the processor. In that case, the presumption is that either a software flaw or hardware problem has caused the CPU to misbehave. Rather than diagnose the problem, the system is reset to get it operational as quickly as possible.

# 39. What is the use of A/D and D/Converters? (Remembering) (CO2)

Analog/digital (A/D) and digital/analog (D/A) converters (typically known as ADCs and DACs, respectively) are often used to interface nondigital devices to embedded systems.

# 40. What is the use of keyboard? (Remembering) (CO2)

A keyboard is basically an array of switches, but it may include some internal logic to help simplify the interface to the microprocessor.

# 41. What is the use of LED's? (Remembering) (CO2)

**Light-emitting diodes (LEDs)** are often used as simple displays by themselves, and arrays of LEDs may form the basis of more complex displays.

#### 42. What is framed buffer? (Remembering) (CO2)

A **frame buffer** is a RAM that is attached to the system bus. The microprocessor writes values into the frame buffer in whatever order is desired. The pixels in the frame buffer are generally written to the display in **raster order** by reading pixels sequentially.

#### 43. Distinguish passive matrix and active matrix. (Analyzing) (CO2)

Early LCD panels were called **passive matrix** because they relied on a two-dimensional grid of wires to address the pixels. Modern LCD panels use an **active matrix** system that puts a transistor at each pixel to control access to the LCD. Active matrix displays provide higher contrast and a higher-quality display.

# 44. What is touchscreen? (Remembering) (CO2)

A **touchscreen** is an input device overlaid on an output device. The touchscreen registers the position of a touch to its surface. By overlaying this on a display, the user can react to information shown on the display.

45. List the types of touchscreen. (Remembering) (CO2)

The two most common types of touchscreens are resistive and capacitive.

# 46. What are the types of component interfacing? (Remembering) (CO2)

Memory Interfacing, Device Interfacing.

#### 47. How I/O devices are designed in device interfacing?(Remembering) (CO2)

Some I/O devices are designed to interface directly to a particular bus, forming *glueless interfaces*. But *glue logic* is required when a device is connected to a bus for which it is not designed.

# 48. List out the elements which included in the architecture of an embedded computing system.(Remembering) (CO2)

Hardware elements, Software elements.

# 49. What are the elements included in hardware architecture?(Remembering) (CO2)

CPU,Bus,Memory,Input and Output devices

# 50. Define Evaluation boards.(Remembering) (CO2)

At the board level, the first step is to consider *evaluation boards* supplied by the microprocessor manufacturer or another company working in collaboration with the manufacturer. Evaluation boards are sold for many microprocessor systems; they typically include the CPU, some memory, a serial link for downloading programs, and some minimal number of I/O devices.

# 51. Show the Hardware architecture of a typical PC.(Remembering) (CO2)

# 52. Define Peripheral Component Interconnect(PCI) (Remembering) (CO2)

**PCI** (*Peripheral Component Interconnect*) is the dominant high-performance system bus . PCI uses high-speed data transmission techniques and efficient protocols to achieve high throughput. PCI uses wide buses with many data and address bits along with multiple control bits.

# 53. Define Target(Remembering) (CO2)

The hardware on which the code will finally run is known as the **target**. The host and target are frequently connected by a USB link, but a higher-speed link such as Ethernet can also be used. The target must include a small amount of software to talk to the host system.

# 54. Explain about Cross compiler? (Understanding)(CO2)

A *cross-compiler* is a compiler that runs on one type of machine but generates code for another. After compilation, the executable code is downloaded to the embedded system by a serial link or perhaps burned in a PROM and plugged in and also often make use of host-target debuggers, in which the basic hooks for debugging are provided by the target and a more sophisticated user interface is created by the host.

#### 55. What is meant by test bench program?(Remembering) (CO2)

A **test bench program** is built to help debug the embedded code. The **test bench** generates inputs to simulate the actions of the input devices; it may also take the output values and compare them against expected values.

### 56. Define Breakpoint(Remembering) (CO2)

**Breakpoint** is a debugging tool, which helps the user to specify an address at which the program's execution is to break. When the PC reaches that address, control is returned to the monitor program. From the monitor program, the user can examine and/or modify CPU registers, after which execution can be continued. Implementing breakpoints does not require using exceptions or external devices.

#### 57. What is Logical analyzer?(Remembering) (CO2)

• The logic analyzer records the values on the signals into an internal memory and then displays the results on a display once the memory is full or the run is aborted. The logic analyzer can capture thousands or even millions of samples of data on all of these channels, providing a much larger time window into the operation of the machine than is possible with a conventional oscilloscope.

• A typical logic analyzer can acquire data in either of two modes that are typically called **state** and **timing modes**.

# 58. What are the debugging challengers?(Remembering) (CO2)

The debugging challengers includes,

- Logical errors in software can be hard to track down, but errors in real-time code can create problems that are even harder to diagnose.

- Real-time programs are required to finish their work within a certain amount of time; if they run too long, they can create very unexpected behavior.

59. List and explain the components used in embedded software.(Remembering) (CO2)

State machine, Circular buffer and queues.

**Circular Buffer**: The circular buffer is a data structure that lets us handle streaming data in an efficient way.

**Queues:** Queues are used whenever data may arrive and depart at somewhat unpredictable times or when variable amounts of data may arrive. A queue is often referred to as an **elastic buffer.**

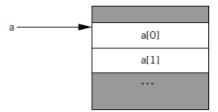

# 60. List out the types of models of programs.(Remembering) (CO2)

- Data flow graphs

- Control/Data flow graphs